#### IEC 62014-5

Edition 1.0 2015-03

### INTERNATIONAL IEEE Std 1734™-2011 STANDARD

Quality of Electronic and Software Intellectual Property Used in System and System on Chip (SoC) Designs

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ISBN 978-2-83222-386-4

Warning! Make sure that you obtained this publication from an authorized distributor.

#### Contents

| 1. Overview                                           | 1  |

|-------------------------------------------------------|----|

| 1.1 Scope                                             | 1  |

| 1.2 Purpose                                           | 1  |

| 1.3 Design environment                                |    |

| 1.4 QIP-compliant enabled implementations             |    |

| 1.5 Conventions used.                                 |    |

| 1.6 Use of color in this standard                     | 6  |

| 1.7 Contents of this standard                         | 6  |

| 2. Normative references                               | 7  |

| 3. Definitions, acronyms, and abbreviations           | 7  |

| 3.1 Definitions                                       |    |

| 3.2 Acronyms and abbreviations                        | 8  |

| 4. Interoperability use model                         | 8  |

| 4.1 Roles and responsibilities                        | 9  |

| 4.2 IP exchange flows                                 | 9  |

| 5. QIP schema structures                              | 10 |

| 5.1 QIP schema structure for golden XML               | 10 |

| 5.2 QIP schema structure for the answer XML           | 14 |

| 5.3 Tooling requirements for operating on golden XML  | 16 |

| 5.4 Relationship between golden XML and completed XML |    |

| 5.5 User extensions                                   | 21 |

| 6. Compatibility with VSIA QIP                        | 22 |

| Annex A (informative) Bibliography                    | 24 |

| Annex B (normative) Semantic consistency rules        | 25 |

| Annex C (informative) IEEE List of Participants       | 32 |

|                                                       |    |

## QUALITY OF ELECTRONIC AND SOFTWARE INTELLECTUAL PROPERTY USED IN SYSTEM AND SYSTEM ON CHIP (SOC) DESIGNS

#### **FOREWORD**

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation.

IEEE Standards documents are developed within IEEE Societies and Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board. IEEE develops its standards through a consensus development process, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of IEEE and serve without compensation. While IEEE administers the process and establishes rules to promote fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards. Use of IEEE Standards documents is wholly voluntary. IEEE documents are made available for use subject to important notices and legal disclaimers (see <a href="http://standards.ieee.org/IPR/disclaimers.html">http://standards.ieee.org/IPR/disclaimers.html</a> for more information).

IEC collaborates closely with IEEE in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees. The formal decisions of IEEE on technical matters, once consensus within IEEE Societies and Standards Coordinating Committees has been reached, is determined by a balanced ballot of materially interested parties who indicate interest in reviewing the proposed standard. Final approval of the IEEE standards document is given by the IEEE Standards Association (IEEE-SA) Standards Board.

- 3) IEC/IEEE Publications have the form of recommendations for international use and are accepted by IEC National Committees/IEEE Societies in that sense. While all reasonable efforts are made to ensure that the technical content of IEC/IEEE Publications is accurate, IEC or IEEE cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications (including IEC/IEEE Publications) transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC/IEEE Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC and IEEE do not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC and IEEE are not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or IEEE or their directors, employees, servants or agents including individual experts and members of technical committees and IEC National Committees, or volunteers of IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board, for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC/IEEE Publication or any other IEC or IEEE Publications.

- 8) Attention is drawn to the normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that implementation of this IEC/IEEE Publication may require use of material covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. IEC or IEEE shall not be held responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patent Claims or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility.

Ìν

International Standard IEC 62014-5/ IEEE Std 1734-2011 has been processed through IEC technical committee 91: Electronics assembly technology, under the IEC/IEEE Dual Logo Agreement.

The text of this standard is based on the following documents:

| IEEE Std    | FDIS         | Report on voting |

|-------------|--------------|------------------|

| 1734 (2011) | 91/1208/FDIS | 91/1227/RVD      |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

The IEC Technical Committee and IEEE Technical Committee have decided that the contents of this publication will remain unchanged until the stability date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- · reconfirmed,

- withdrawn,

- · replaced by a revised edition, or

- · amended.

# IEEE Standard for Quality of Electronic and Software Intellectual Property Used in System and System on Chip (SoC) Designs

Sponsor

**Design Automation Standards Committee** of the **IEEE Computer Society**

Approved 16 June 2011

**IEEE-SA Standards Board**

This standard contains material originally published by the VSI Alliance and currently available in the public domain (http://vsi.org/). Acknowledgment is made to the VSI Alliance, who developed the VSIA-QIP v4.0 spreadsheet and macros, and the QIP Metric Users Guide Version 4.0 document from which some material in this standard was derived.

**Abstract:** A standard XML format for representing electronic design intellectual property (IP) quality information, based on an information model for IP quality measurement, is defined. It includes a schema and the terms that are relevant for measuring IP quality, including the software that executes on the system. The schema and information model can be focused to represent particular categories of interest to IP users. In the context of this document, the term *IP* shall be used to mean *electronic design intellectual property*. Electronic design intellectual property is a term used in the electronic design community to refer to a reusable collection of design specifications that represent the behavior, properties, and/or representation of the design in various media.

**Keywords:** AMS, analog and mixed signal, design environment, EDA, electronic design automation, electronic system level, ESL, IEEE 1734, implementation constraints, MEMS, microelectromechanical systems, QIP, Quality IP metrics, register transfer logic, RTL, SCRs, semantic consistency rules, use models, verification IP, VIP, XML design meta data, XML schema

Verilog is a registered trademark of Cadence Design Systems, Inc. in the United States and/or other jurisdictions.

W3C is a registered trademark of the World Wide Web Consortium (registered in numerous countries). Marks of W3C are registered and held by its host institutions: Massachusetts Institute of Technology (MIT), European Research Consortium for Information and Mathematics (ERCIM), and Keio University, Japan.

#### **IEEE Introduction**

This introduction is not part of IEEE Std 1734-2011, IEEE Standard for Quality of Electronic and Software Intellectual Property Used in System and System on Chip (SoC) Designs.

The purpose of this standard is to provide a unified view of quality measures for *electronic design intellectual property* (IP) to facilitate the use and integration of IP used in electronic system design. These quality measures can be evaluated in the context of the end application to help determine suitability and plan mitigation measures for potential integration gaps. This can enable the continuous improvement of IP used for system design and verification by providing a mechanism for qualitative comparison between such IP. The standard IP quality measures and characteristic exchange format defined can be incorporated into a variety of electronic design automation (EDA) tools. The goal of this specification is to specify a quality standard metric that will account for the variances in designing, verifying and testing the IP, which will result in fair quality assessment, reducing the risk of schedule slip or mask spins due to faulty IP.

The working group consisted of electronic system, IP provider, semiconductor, and EDA companies, and used the VSI Alliance Quality IP (QIP) metric as a baseline for the metrics. The data specified by the standard is extensible in locations specified in the schema. This structure can be used as the basis of both manual and automatic methodologies.

This standardization project provides electronic design and SoC engineers with a well-defined standard that meets their requirements in evaluating and validating IP and enables a step function increase in their productivity. This project also provides the EDA industry with a standard to which they can adhere and that they can support in order to deliver their solutions in this area.

#### **Notice to users**

#### Laws and regulations

Users of these documents should consult all applicable laws and regulations. Compliance with the provisions of this standard does not imply compliance to any applicable regulatory requirements. Implementers of the standard are responsible for observing or referring to the applicable regulatory requirements. IEEE does not, by the publication of its standards, intend to urge action that is not in compliance with applicable laws, and these documents may not be construed as doing so.

#### Copyrights

This document is copyrighted by the IEEE. It is made available for a wide variety of both public and private uses. These include both use, by reference, in laws and regulations, and use in private self-regulation, standardization, and the promotion of engineering practices and methods. By making this document available for use and adoption by public authorities and private users, the IEEE does not waive any rights in copyright to this document.

#### **Updating of IEEE documents**

Users of IEEE standards should be aware that these documents may be superseded at any time by the issuance of new editions or may be amended from time to time through the issuance of amendments, corrigenda, or errata. An official IEEE document at any point in time consists of the current edition of the document together with any amendments, corrigenda, or errata then in effect. In order to determine whether a given document is the current edition and whether it has been amended through the issuance of amendments, corrigenda, or errata, visit the IEEE Standards Association web site at <a href="http://ieeexplore.ieee.org/xpl/standards.jsp">http://ieeexplore.ieee.org/xpl/standards.jsp</a>, or contact the IEEE at the address listed previously.

For more information about the IEEE Standards Association or the IEEE standards development process, visit the IEEE-SA web site at <a href="http://standards.ieee.org">http://standards.ieee.org</a>.

#### **Errata**

Errata, if any, for this and all other standards can be accessed at the following URL: <a href="http://standards.ieee.org/findstds/errata/index.html">http://standards.ieee.org/findstds/errata/index.html</a>. Users are encouraged to check this URL for errata periodically.

#### Interpretations

Current interpretations can be accessed at the following URL: <a href="http://standards.ieee.org/findstds/">http://standards.ieee.org/findstds/</a> interps/index.html.

#### **Patents**

Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE is not responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patents Claims or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility. Further information may be obtained from the IEEE Standards Association.

## Quality of Electronic and Software Intellectual Property Used in System and System on Chip (SoC) Designs

IMPORTANT NOTICE: This standard is not intended to ensure safety, security, health, or environmental protection. Implementers of the standard are responsible for determining appropriate safety, security, environmental, and health practices or regulatory requirements.

This IEEE document is made available for use subject to important notices and legal disclaimers. These notices and disclaimers appear in all publications containing this document and may be found under the heading "Important Notice" or "Important Notices and Disclaimers Concerning IEEE Documents." They can also be obtained on request from IEEE or viewed at <a href="http://standards.ieee.org/IPR/disclaimers.html">http://standards.ieee.org/IPR/disclaimers.html</a>.

#### 1. Overview

#### 1.1 Scope

This specification defines a standard XML format for representing electronic design intellectual property (IP) quality information, based on an information model for IP quality measurement. It includes a schema and the terms that are relevant for measuring IP quality, including the software that executes on the system. The schema and information model can be focused to represent particular categories of interest to IP users. In the context of this document, the term *IP* shall be used to mean *electronic design intellectual property*. Electronic design intellectual property is a term used in the electronic design community to refer to a reusable collection of design specifications that represent the behavior, properties, and/or representation of the design in various media.

#### 1.2 Purpose

The purpose of this standard is to provide a unified view of quality measures for IP to facilitate the use and integration of this IP used in electronic system design. This will enable the continuous improvement of IP used for system design and verification by providing a mechanism for qualitative comparison between such

IP. The standard IP quality measures and characteristic exchange format defined can be incorporated into a variety of electronic design automation (EDA) tools.

#### 1.3 Design environment

The IP quality specification is a mechanism to express and exchange information about design IP, its development, data management, documentation, verification and validation processes, as well as evaluating the quality and stability of the owning or development organization. While the XML description formats are the core of this standard, describing the quality specification in the context of its basic use model, the design environment (DE), more readily depicts the extent and limitations of the semantic intent of the data. The DE coordinates a set of tools and IP, or expressions of that IP (e.g., models), through the evaluation and manipulation of metadata descriptions of the IP such that the IP can be efficiently integrated into and SoC and reused.

#### 1.3.1 Design intellectual property

Quality IP (QIP) is structured around the concept of IP reuse. Electronic design intellectual property, or IP, is a term used in the electronic design community to refer to a reusable collection of design specifications that represent the behavior, properties, and/or representation of the design in various media. The name IP is partially derived from the common practice of considering a collection of this type to be the intellectual property of one party. Both hardware and software collections are encompassed by this term.

Examples of these collections may include the following:

- Design objects—This can include the following: a)

- Fixed HDL descriptions: Verilog<sup>®</sup>, VHDL<sup>1</sup> 1)

- Verification IP descriptions: Verilog (see IEEE Std 1364<sup>TM</sup> [B2], IEC/IEEE 61691-1-1 [B1])<sup>2</sup> 2)

- 3) Hardened IP descriptions: GDSII, LEF, LIB, LVS, Characterization Reports

- 4) Software descriptions: C, C++, etc.

- HDL-specified verification IP (e.g., basic stimulus generators and checkers) 5)

- IP views—This is a list of different views (levels of description and/or languages) to describe the IP object. These views include the following:

- 1) Design view: RTL Verilog or VHDL, flat or hierarchical components

- 2) Simulation view: model views, targets, simulation directives, etc.

- Documentation view: standard, user guide, etc. 3)

- Supporting scripts: synthesis, makefile, manufacturing test, etc. 4)

#### 1.4 QIP-compliant enabled implementations

Complying with the rules outlined in this subclause allows the provider of tools or IP to class their products as *QIP compliant*. Conversely, any violation of these rules removes that naming right. This subclause first

<sup>&</sup>lt;sup>1</sup> Verilog is a registered trademark of Cadence Design Systems, Inc. in the United States and/or other jurisdictions. This information is given for the convenience of users of this standard and does not constitute an endorsement by the IEEE of these products. Equivalent products may be used if they can be shown to lead to the same results.

The numbers in brackets correspond to that of the bibliography in Annex A

introduces the set of metrics for measuring the valid use of the specifications. It then specifies when those validity checks are performed by the various classes of products and providers: DEs, point tools, and IPs.

- a) Parse validity

- 1) Parsing correctness: Ability to read all QIP descriptions.

- 2) Parsing completeness: Cannot require information that could be expressed in a QIP format to be specified in a non-QIP format. Processing of all information present in a QIP document is not required.

- b) Description validity

- 1) Schema correctness: Metrics are described using XML files that conform to the QIP schema.

- 2) Usage completeness: Extensions to the QIP schema shall only be used to express information that is not currently described in QIP. This information shall be forwarded to the IEEE 1734 committee for potential inclusion in a later release.

- c) Semantic validity

- Semantic correctness: Adheres to the semantic interpretations of QIP data described in this standard.

- 2) Semantic completeness: Obeys all the semantic consistency rules described in Annex B.

These validity rules can be combined with the product class specific rules to cover the full QIP-enabled space. The following subclauses describe the rules a provider has to check to claim a tool or DE is QIP compliant.

A QIP-compliant DE or point tool may read descriptions based on multiple versions of the QIP schema. If the DE or point tool does provide this capability, the effect shall be as if all of the descriptions had been translated by an XSL Transform (XSLT), which converts descriptions from one version to the next.

#### 1.4.1 Design environments

A QIP-enabled DE:

- a) Shall follow the parse validity requirements shown in 1.4.

- b) Shall do so without losing any preexisting information when modifying any existing QIP descriptions. In particular, it shall preserve any vendor extension data included in the existing QIP description.

#### 1.5 Conventions used

The conventions used throughout the document are included here.

QIP schema is case-sensitive.

#### 1.5.1 Visual cues (meta-syntax)

**Bold** shows required keywords and/or special characters, e.g., addressSpace. For the initial definitional use (per element), keywords are shown in **boldface-red** text, e.g., **bitsInLau** (see also 1.6).

Bold italics shows group names or data types, e.g., nameGroup or boolean.

Courier shows examples, external command names, directories and files, etc., e.g., address 0x0 is on D[31:0].

#### 1.5.2 Notational conventions

The keywords *required, shall, shall not, should, should not, recommended, may,* and *optional* in this document are to be interpreted as described in the IETF Best Current Practices document 14, RFC 2119 [B4].

#### 1.5.3 Syntax examples

Any syntax examples shown in this standard are for information only and are only intended to illustrate the use of such syntax.

#### 1.5.4 Graphics used to document the schema

The W3C® Web site specifies the XML schema language used to define the QIP XML schemas.<sup>3, 4, 5</sup> Normative details for compliance to the QIP standard are contained in the schema files. Within this document, pictorial representations of the information in the schema files illustrate the structure of the schema and define any constraints of the standard. With the exception of scope and visibility issues, the information in the figures and the schema files is intended to be identical. Where the figures and schema are in conflict, the XML schema file shall take precedence.

#### 1.5.4.1 Elements and attributes

The element is the fundamental building block on which this standard is based. An element may be either a leaf element, which is a container for information, or a branch element, which may contain further branch elements or leaf elements.

A leaf or branch element may also contain attributes. Attributes are containers for information within the containing element.

#### 1.5.4.2 Types

A type is a designation of the format for the contents of an element or attribute. There are two different styles of types that can be defined. A type may be assigned to a leaf element or an attribute. This type is called a simpleType and defines the format of data that may be stored in this container. A type may also be assigned to a branch element. This type is called a complexType and defines further elements and attributes contained in the branch element.

<sup>&</sup>lt;sup>3</sup> The XML schema specification is available at http://www.w3.org/TR/2004/REC-xmlschema-1-20041028.

<sup>&</sup>lt;sup>4</sup> W3C is a registered trademark of the World Wide Web Consortium (registered in numerous countries). Marks of W3C are registered and held by its host institutions: Massachusetts Institute of Technology (MIT), European Research Consortium for Information and Mathematics (ERCIM), and Keio University, Japan. This information is given for the convenience of users of this standard and does not constitute an endorsement by the IEEE of these products. Equivalent products may be used if they can be shown to lead to the same results.

<sup>&</sup>lt;sup>5</sup> Information on references can be found in Clause 2.

#### 1.5.4.3 Diagrams

The diagrams used throughout this standard graphically detail the organization the elements and attributes.

#### 1.5.4.3.1 Elements and sequences

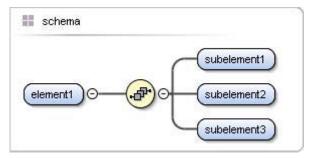

Figure 1 shows the sequence-compositor. At the left is a branch element, element1 is connected to a sequence-compositor. The sequence-compositor defines the order the subelements appear in the branch element. **subElement1** shall appear first inside of **element1**. This is followed by **subElement2** and **subElement3** before closing **element1**.

Figure 1—Sequence compositor

#### 1.5.4.3.2 Elements and choices

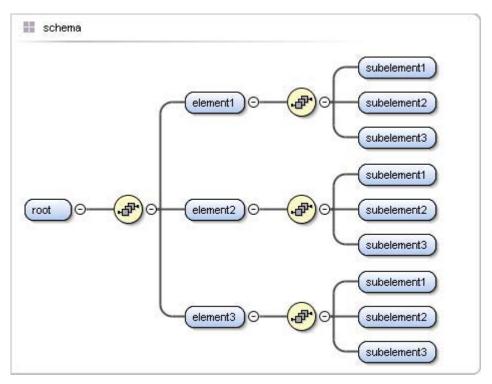

Figure 2 shows the variations of the choice-compositor. **root** is connected to a choice-compositor. The choice-compositor specifies that one of the elements on the right side shall be chosen. **root** may contain one of the following: **element1**, **element2**, or **element3**. Each subelement is also connected to a choice-compositor.

Figure 2—Choice compositor variations

#### 1.6 Use of color in this standard

This standard uses a minimal amount of color to enhance readability. The coloring is not essential and does not affect the accuracy of this standard when viewed in pure black and white. The places where color is used are the following:

- Cross references that are hyperlinked to other portions of this standard are shown in <u>underlined-blue</u> text (hyperlinking works when this standard is viewed interactively as a PDF file).

- Syntactic keywords and tokens in the formal language definitions are shown in boldface-red text.

#### 1.7 Contents of this standard

The organization of the remainder of this standard is as follows:

- Clause 2 provides references to other applicable standards that are assumed or required for this standard.

- Clause 3 defines terms, acronyms, and abbreviations used throughout the different specifications contained in this standard.

- Clause 4 defines the use model.

- Clause 5 describes the schema structure.

- Clause 6 describes the compatability with and differences from the VSIA QIP.

#### 2. Normative references

The following referenced documents are indispensable for the application of this document (i.e., they must be understood and used, so each referenced document is cited in text and its relationship to this document is explained). For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments or corrigenda) applies.

W3C, XML Schema, 12 September 2005.6

W3C, XML Schema, Part 1: Structures, Second Edition, W3C Recommendation, 28 October 2004.

<sup>7</sup> This specification is available at: http://www.w3.org/TR/2004/REC-xmlschema-1-20041028.

<sup>&</sup>lt;sup>6</sup> This specification is available at: http://www.w3.org/2001/XMLSchema; http://www.w3.org/2001/XMLSchema-instance.